本文轉(zhuǎn)自Agilent(安捷倫)官方網(wǎng)站,原文作者李凱����。本文簡要地介紹了PCI-e 3.0的知識,并詳細描述了PCI-e 3.0的測試方法���,對于從事高速數(shù)字電路設(shè)計的讀者來說��,是一篇很有參考價值的文章�。

1. 前言

PCI Express(簡稱PCI-e)總線是PCI總線的串行版本����,其采用多對高速串行的差分信號進行高速傳輸,每對差分線上的信號速率可以是1代的2.5Gbps���、2代的5Gbps以及現(xiàn)在正逐漸開始應用的3代8Gbps����。

PCI-e標準是由PCI-SIG組織制定,自從推出以來���,1代和2代標準已經(jīng)在PC和Server上逐漸普及�,用于支持高速顯卡以及其它接口卡對于高速數(shù)據(jù)傳輸?shù)囊?���。出于支持更高總線數(shù)據(jù)吞吐率的目的,PCI-SIG組織在2010年制定了PCI-e 3.0���,即PCI-e 3代的規(guī)范�����。目前,PCI-e 3.0已經(jīng)開始出現(xiàn)在一些高端的Server上��,而在普通PC上的應用也是指日可待�。

那么PCI-e 3.0總線究竟有什么特點?對于其測試有什么特殊的地方呢��?我們這里就來探討一下��。

2. PCI-e 3.0簡介

2.1 信號速率的變化

首先我們看一下制定PCI-e 3代規(guī)范的目的�,其目的主要是要在現(xiàn)有的FR4板材和接插件的基礎(chǔ)上提供比PCI-e 2代高一倍的有效數(shù)據(jù)傳輸速率���,同時保持和原有1代、2代設(shè)備的兼容�。別看這是個簡單的目的,但實現(xiàn)起來可不容易�。

我們知道,PCI-e 2代在每對差分線上的數(shù)據(jù)傳輸速率是5Gbps��,相對于1代提高了1倍��;而3代要相對于2代把速率也提高一倍��,理所當然的是把數(shù)據(jù)傳輸速率提高到10Gbps��。但是就是這個10Gbps把PCI-SIG給難住了����,因為PC和Server上出于成本的考慮,普遍使用便宜的FR4的PCB板材以及廉價的接插件�,無論采用什么技術(shù)都很難保證10Gbps的信號還能在原來的信號路徑上可靠地傳輸很遠的距離(典型距離是15~30cm)。因此PCI-SIG最終決定把PCI-e 3代的數(shù)據(jù)傳輸速率定在8Gbps�����。但是8Gbps比著2代的5Gbps并沒有高一倍�,所以PCI-SIG決定在3代標準中把在1代和2代中使用的8b/10b編碼去掉����。我們知道��,在PCI-e 1代和2代中為了保證數(shù)據(jù)的傳輸密度�����、直流平衡以及內(nèi)嵌時鐘的目的���,每8bit數(shù)據(jù)會編碼成10bit數(shù)據(jù)傳輸�����。因此����,5Gbps的實際有效數(shù)據(jù)傳輸速率是5Gbps×8b/10b=4Gbps�����。這樣��,如果在PCI-e 3代中不使用8b/10b編碼���,其有效數(shù)據(jù)傳輸速率就能比著 2代的4Gbps提高1倍����。但是這樣問題又來了��,數(shù)據(jù)如果不經(jīng)編碼傳輸很難保證數(shù)據(jù)傳輸密度和直流平衡��,接收端的時鐘恢復電路也很容易失鎖���,于是PCI-e 3代里面采用了擾碼的方法����,即數(shù)據(jù)傳輸前先和一個多項式進行異或��,這樣傳輸鏈路上的數(shù)據(jù)就看起來比較有隨機性�,到了接收端再用相同的多項式把數(shù)據(jù)恢復出來。通過上述方法���,PCI-e 3代可以用8Gbps的傳輸速率實現(xiàn)比2代的5Gbps高1倍的數(shù)據(jù)傳輸速率����。

2.2 發(fā)送端的變化

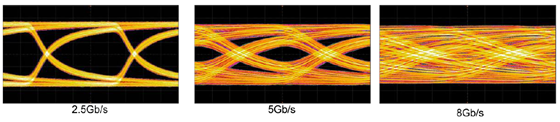

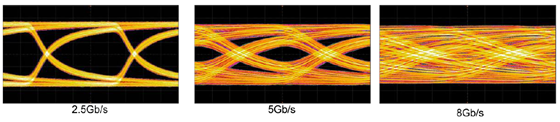

但是問題遠沒有結(jié)束��,即使數(shù)據(jù)速率只有8Gbps,要在原有的廉價PCB和接插件上實現(xiàn)可靠傳輸也還要解決一些新的問題�����。其中最大的問題是信號的損耗���,F(xiàn)R4板材對信號高頻成分有很大衰減�����,而信號速率越高����,其高頻成分越多��,所以衰減也就更厲害�����。下圖是不同速率的信號經(jīng)過10英寸的FR4板材的PCB傳輸以后信號的眼圖���,我們可以看到8Gbps的信號在接收端基本上看不到眼圖了,更不要說進行有效的數(shù)據(jù)接收����。

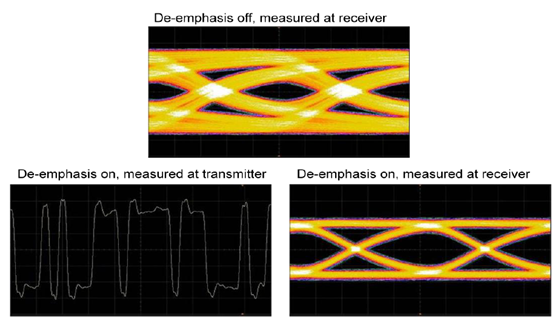

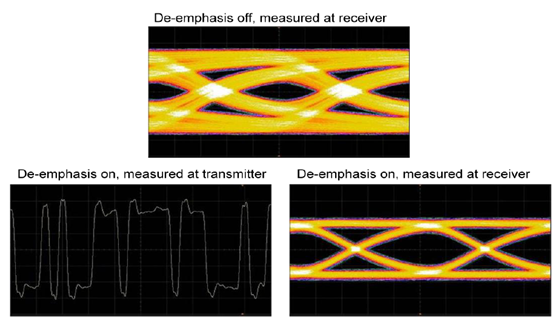

為了解決這個問題�,在PCI-e的1代和2代中使用了去加重(De-emphasis)技術(shù)���,即信號的發(fā)射端(TX)在發(fā)送信號時對跳變bit(代表信號中的高頻成分)加大幅度發(fā)送��,這樣可以部分補償一下傳輸線路對高頻成分的衰減����,從而得到比較好的眼圖�。

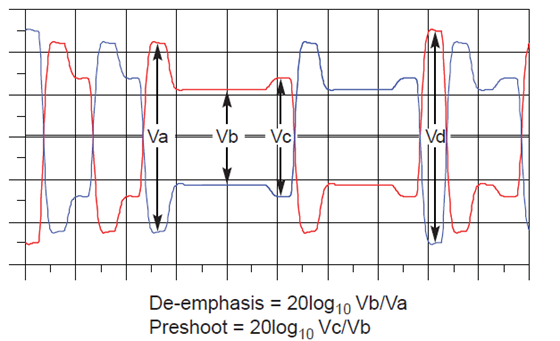

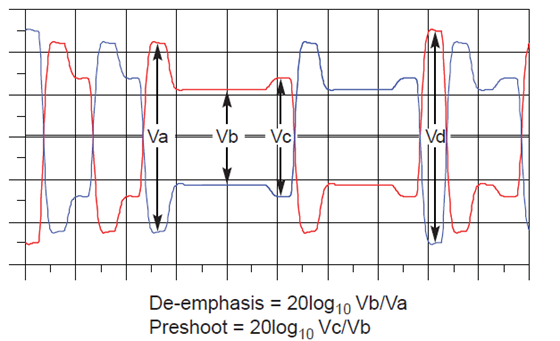

PCI-e 1代中采用了-3.5db的去加重,PCI-e 2代中采用了-3.5db和-6db的去加重�����, 而對于3代來說�,由于信號速率更高,需要采用更加復雜的2階去加重技術(shù)����。即除了跳變bit增大幅度發(fā)送(De-emphasis)以外,在跳變bit的前1個bit也要增大幅度發(fā)送����,這個增大的幅度通常叫做Preshoot�。

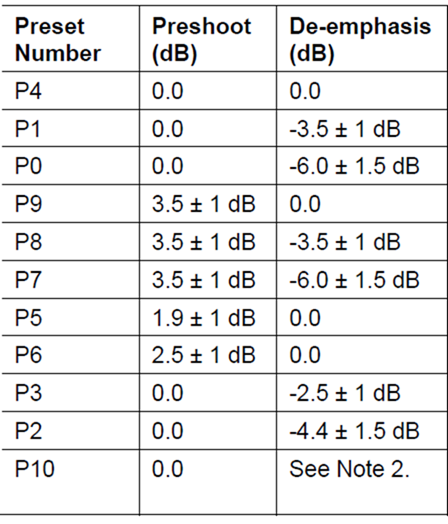

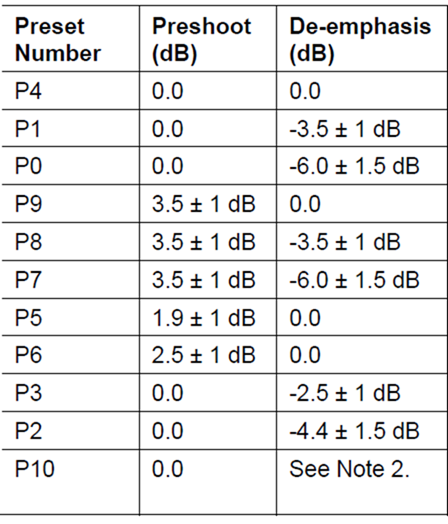

為了應對復雜的鏈路環(huán)境����,PCI-e 3代中規(guī)定了共11種不同的Preshoot和De-emphasis的組合(Preset),實際應用中Tx和Rx端可以在Link Training階段協(xié)商出一個最優(yōu)的Preset值��。

2.3 接收端的變化

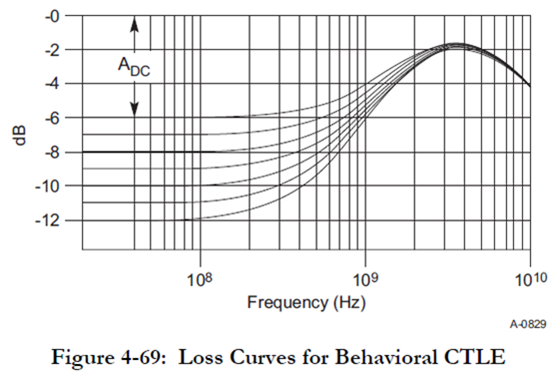

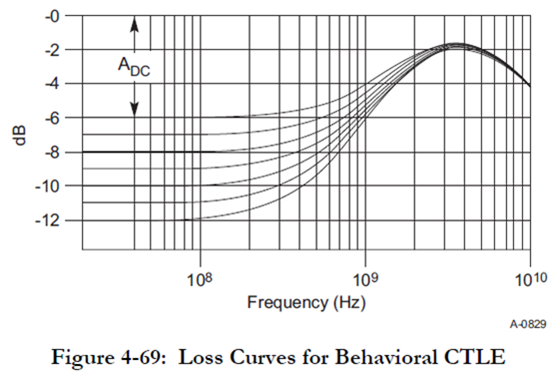

那做了這些工作就夠了嗎�����?經(jīng)過實驗發(fā)現(xiàn)�����,僅僅在發(fā)送端對信號高頻進行補償還是不夠��,如是PCI-e 3代標準中又規(guī)定在接收端(RX端)還要對信號做均衡(Equalization)�。所謂均衡,就是在RX端的接收芯片內(nèi)部增加一個均衡電路�,這個均衡電路可以抬高接收到的信號中的高頻分量,從而對線路的損耗進行進一步的補償��。均衡電路的實現(xiàn)難度較大���,以前主要用在通信設(shè)備的背板或長電纜傳輸?shù)膱龊?���,現(xiàn)在也逐漸開始在計算機領(lǐng)域應用���,比如USB3.0中也采用了均衡技術(shù)����。下圖是PCI-e 3.0里對均衡器的頻響特性的要求�����。我們可以看到均衡器的強弱也有很多檔可選����,在Link Training階段TX和RX端會協(xié)商出一個最佳的組合。

我們看到�,經(jīng)過種種努力,PCI-e 3.0總算初步實現(xiàn)了其初衷���,即在現(xiàn)有的FR4板材和接插件的基礎(chǔ)上提供比PCI-e 2代高一倍的有效數(shù)據(jù)傳輸速率��。但我們同時也看到�����,PCI-e 3代的芯片會變得更加復雜�����,系統(tǒng)設(shè)計的難度也也更大�����。如何保證PCI-e 3代總線工作的可靠性和很好的兼容性�,就成為設(shè)計和測試人員面臨的嚴峻挑戰(zhàn)。

3. PCI-e 3.0的測試

首先要說明的一點是�,由于PCI-e 3代目前只頒布了Base的規(guī)范(即芯片規(guī)范),但CEM規(guī)范(即主板和插卡的規(guī)范)和測試規(guī)范還沒有正式發(fā)布��,所以下面介紹的方法是基于目前的通用做法�����,以后隨著規(guī)范的正式發(fā)布�,具體測試方法可能還有變化。

3.1 發(fā)送端的信號質(zhì)量測試

對于發(fā)送端的測試���,主要是用寬帶示波器捕獲其發(fā)出的信號并驗證其信號質(zhì)量滿足規(guī)范要求��。按照目前Base規(guī)范中的要求�,PCI-e 3.0的測試需要至少12GHz帶寬的示波器,并配合上相應的測試夾具和測試軟件���。

由于PCI-e 3.0的信號經(jīng)過傳輸以后信號幅度都已經(jīng)衰減得很?���。ǖ湫椭凳?00mV左右)��,為了保證足夠的測量精度��,除了示波器的帶寬要足夠以外���,還需要示波器有很低的底噪聲才能保證測量的準確性和測量重復性。Agilent公司的90000X系列示波器除了能夠提供最高到32GHz的硬件帶寬以外�,還具有業(yè)內(nèi)最低的底噪聲指標以及高達2G的存儲深度,可以充分滿足PCI-e 3代測試的要求��,下面是Agilent的90000X示波器的一些主要指標��。

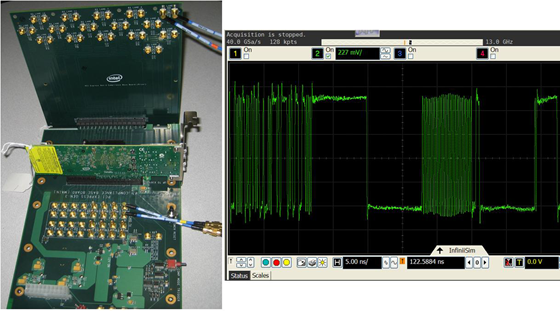

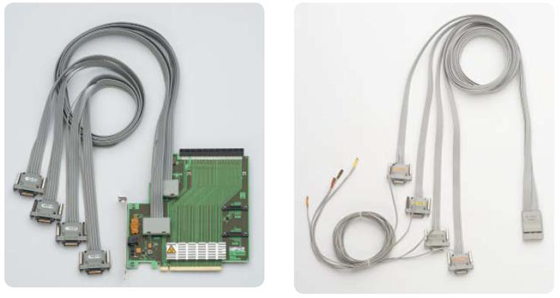

測試中首先使用PCI-SIG提供的PCI-e 3的夾具把被測信號引出(PCI-e 3代的夾具和PCI-e 2代一樣分為CBB板和CLB板�����,CBB板用于插卡的測試,CLB板用于主板的測試)���,然后通過測試夾具上的切換開關(guān)控制DUT輸出PCI-e 3代的一致性測試碼型�����。需要注意的一點是由于PCI-e 3代信號如前所述共有11種Preset值�,測試過程中應明確當前測試的是哪一種Preset值����,做信號質(zhì)量測試常用的有Preset7、Preset8��、Preset1�、Preset0。下圖是PCI-e 3代的CBB板及一致性測試碼型��。

另外��,PCI-e 3代測試很重要的一點是要做信號的的Embed���,Embed即是在測試過程中加入芯片封裝對信號的影響�����,這個芯片封裝的模型是PCI-SIG以S參數(shù)文件的形式提供的����,測試過程中需要示波器能把這個S參數(shù)文件的影響加到被測波形上。同時���,測試過程中示波器是用2個通道分別連接信號的正負端���,要得到最后的差分波形需要示波器對2個通道的波形做相減運算。如果波形相減和S參數(shù)嵌入的工作都由示波器軟件計算�����,會大大影響測試速度���。Agilent公司的90000A/90000X示波器內(nèi)部都有硬件的通道相減及S參數(shù)運算功能,可以大大提高測試的速度和效率���。

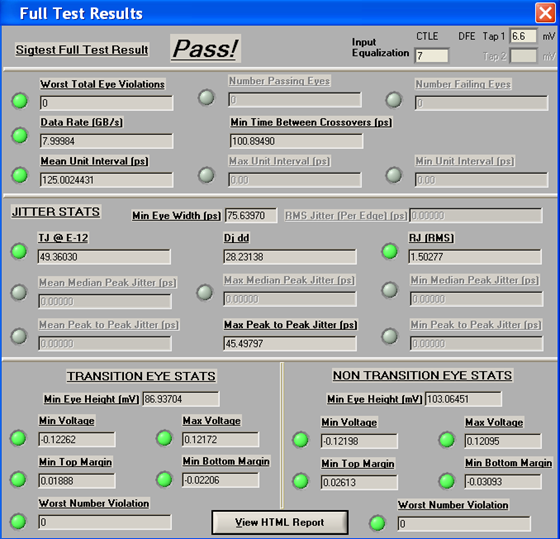

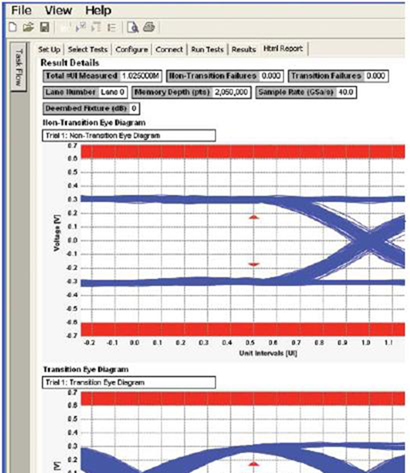

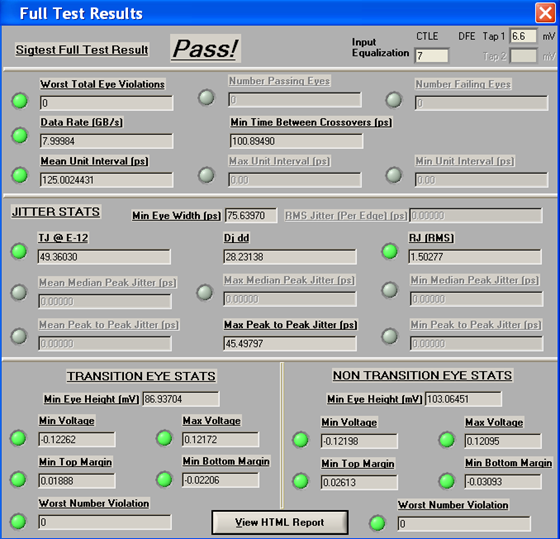

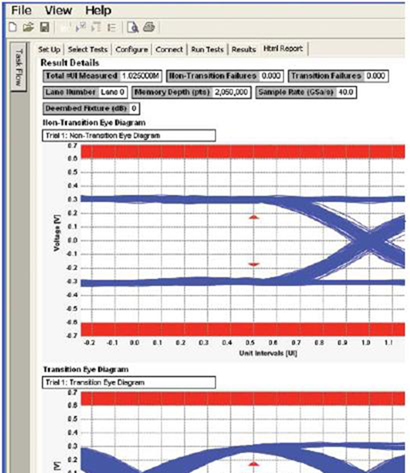

對測試數(shù)據(jù)做分析得方法有2種:一種是使用PCI-SIG提供的Sigtest軟件做手動分析�����,一種是使用Agilent公司提供的N5393C PCI-e 3.0自動一致性測試�����。Sigtest軟件是的算法由PCI-SIG提供�,但是需要用戶手動捕獲數(shù)據(jù)進行后分析。Sigtest可以進行信號的眼圖���、模板��、抖動的測試����。下圖是用Sigtest的測試結(jié)果�。

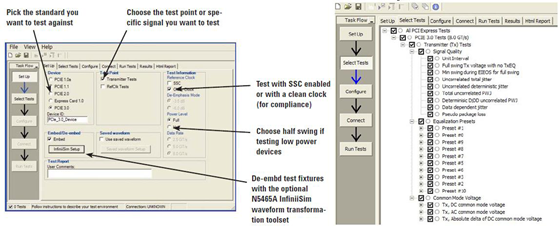

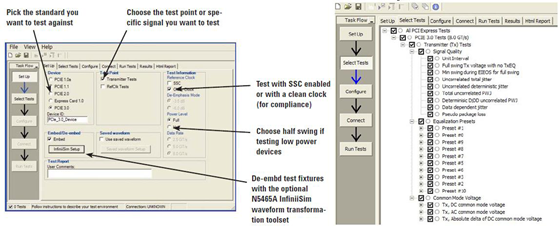

由于Sigtest需要用戶手動捕獲數(shù)據(jù),對于不熟練的測試人員容易可能由于設(shè)置不對造成測試結(jié)果的不一致����,而且其測試項目有限,沒有覆蓋全部的信號要求��。所以針對PCI-e3的測試Agilent還提供了N5393C的自動化測試軟件�����。這個軟件以圖形化的界面指導用戶完成設(shè)置����、 連接和測試過程�����,除了提供Swing���、Preset、Common Mode等更多測試項目以外�,還可以自動進行示波器測量參數(shù)設(shè)置以及自動生成報告,提高了測試的效率和可重復性��。除此以外���,這個軟件在測試過程中還會對被測件發(fā)出的碼型和速率進行檢查���,以確認測試使用的是規(guī)范要求的正確碼型�����。下圖是N5393C軟件的設(shè)置和生成的測試報告�����。

以下是PCI-e 3.0信號測試推薦使用的儀器:

- DSA91304A/DSAX91604A高帶寬實時示波器,用于高速PCI-e 3.0的信號測試

- N5393C PCI-e3測試軟件: 快速進行PCI-e 3.0的信號一致性測試

- N5465A去嵌入軟件:用于封裝和鏈路參數(shù)的嵌入和去嵌入

- CLB3/CBB3 PCI-e 3.0測試夾具�����,用于連接被測設(shè)備��,從PCI-SIG購買

- 其它:SMP-SMA電纜�����、SMP負載等

3.2 接收端的接收容限測試

PCI-e 1.0和2.0的時代�����,接收端測試不是必須的���,通常只要保證發(fā)送端的信號質(zhì)量基本就能保證系統(tǒng)的正常工作��。但是對于PCI-e 3.0來說����,由于速率更高����,發(fā)送端發(fā)出的信號經(jīng)過長線傳輸后信號質(zhì)量總是不會太好����,所以接收端使用了復雜的均衡技術(shù)來提升接收端的接收能力�。由于接收端更加復雜而且其均衡的有效性會顯著影響鏈路傳輸?shù)目煽啃裕虼嗽赑CI-e 3.0時代���,接收端的測試變成了必測的項目����。

所謂接收端測試�,就是要驗證接收端對于惡劣信號的容忍能力。這就涉及到2個問題���,一個是這個惡劣信號怎么定義�,另一個是怎么判斷被測系統(tǒng)能夠容忍這樣的惡劣信號����。

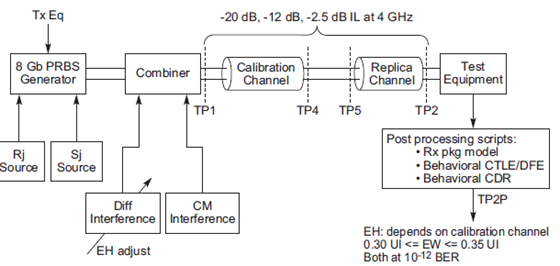

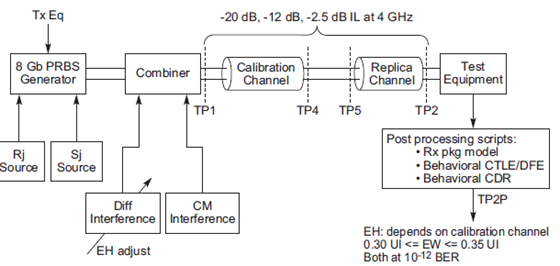

首先來看一下這個惡劣信號的定義����,這不是一個隨便的差信號就可以,這個信號的惡劣程度有精確定義才能保證測量的重復性。這個惡劣信號通常叫做Stress Eye�����,即壓力眼圖���,實際上是借鑒了10G以太網(wǎng)的叫法���。這個Stress Eye實際上是用高性能的誤碼儀先產(chǎn)生一個純凈的帶預加重和Preshoot的8Gbps的信號,然后在這個信號上疊加上精確控制的隨機抖動(RJ)�����、周期抖動(SJ)�����、差模和共模噪聲以及碼間干擾(ISI)�����。為了確定每個成分的大小都符合規(guī)范的要求�����,所以測試之前需要先用示波器對測試信號進行校準,確定產(chǎn)生的是規(guī)范要求的Stress Eye�����。下圖產(chǎn)生Stress Eye和信號校準的一個原理圖�����。

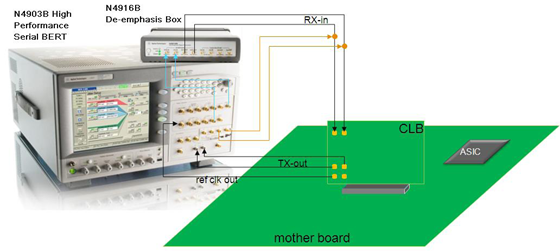

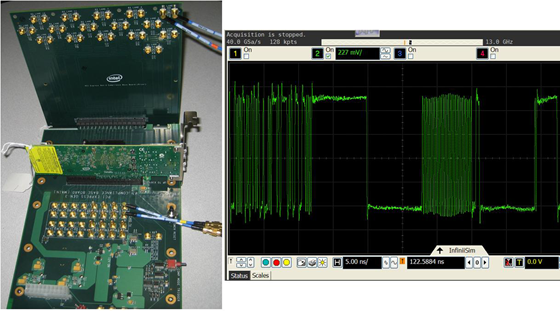

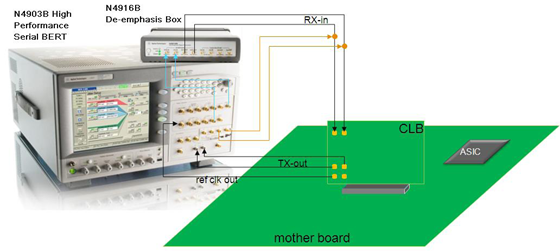

另一個問題是如何判斷被測系統(tǒng)能夠容忍這樣的惡劣信號��。這就需要被測系統(tǒng)工作在環(huán)回模式���,即把其從RX端收到的數(shù)據(jù)再通過TX端發(fā)送出來送回誤碼儀����,誤碼儀通過比較誤碼來判斷數(shù)據(jù)是否被正確接收�����,測試中要求誤碼率小于1E-12��。下圖是用Agilent的高性能串行誤碼儀N4903B和N4916B預加重模塊進行PCI-e 3.0接收測試一個示意圖��。實際測試中根據(jù)實際情況還需要增加一些耦合器��、轉(zhuǎn)接頭�����、測試電纜等����。

這個測試對于激勵源也即碼型發(fā)生器的要求很高。首先其要能產(chǎn)生高質(zhì)量的PCI-e 3.0的8Gbps的數(shù)據(jù)流�,其固有抖動要非常小才不會影響正常的抖動容限測試;其次其要能在數(shù)據(jù)流上調(diào)制上幅度�����、頻率精確可控的抖動分量并能夠進行誤碼檢測�。Agilent的N4903B是高性能的串行誤碼儀,其單路可以產(chǎn)生12.5Gbps的高速數(shù)據(jù)流����,信號20%~80%上升時間<20ps,固有抖動只有9ps(p-p),信號的幅度在50mV~1.8V范圍內(nèi)連續(xù)可調(diào)���,同時其內(nèi)部集成時鐘恢復電路�����,信號接收靈敏度小至50mV����,非常適合PCI-e 3.0接收測試這種速率高同時對信號質(zhì)量又有很好要求的場合。N4903B還可以通過后續(xù)升級支持最高28.4Gbps的高速串行數(shù)據(jù)��,可以充分兼顧未來更高速率的應用�。

除此以外,PCI-e 3.0的接收測試還需要產(chǎn)生帶Preshoot和De-emphasis的信號�����,這實際上是一個2階的De-emphasis��。Agilent的N4916B是高性能的De-emphasis模塊����,其可以產(chǎn)生多達4階、最高幅度到12db的De-emphasis�����,可以充分滿足PCI-e 3.0的接收測試以及未來更高性能總線的要求���。

以下是PCI-e 3.0接收測試推薦的主要設(shè)備:

- N4903B 12.5Gbps高性能誤碼分析儀�,用于產(chǎn)生帶抖動的PCI-e 3.0信號并檢測環(huán)回信號誤碼率

- N4916B預加重模塊, 用于產(chǎn)生測試需要的測試需要的帶Preshoot和De-emphasis的信號

- CLB3/CBB3 PCI-e 3.0測試夾具�����,用于連接被測設(shè)備�,從PCI-SIG購買

- DSA91304A/DSAX91604A高帶寬實時示波器�����,用于測試前校準N4903B產(chǎn)生的信號

- 其它:測試軟件���、測試電纜��、耦合器�、轉(zhuǎn)接頭等

3.3 PCI-e 3.0協(xié)議的測試

完成信號質(zhì)量的測試僅僅是保證了PCI-e物理層的可靠工作��,整個系統(tǒng)的可靠工作還離不開上層協(xié)議的支持����。由于PCI-e 3.0是全新的標準,所以為了幫助用戶更進一步分析和定位由于上層協(xié)議造成的問題���,Agilent還提供了全套的PCI-e 3.0協(xié)議測試方案��,方案中包括了協(xié)議分析儀�����、探頭以及訓練器�。

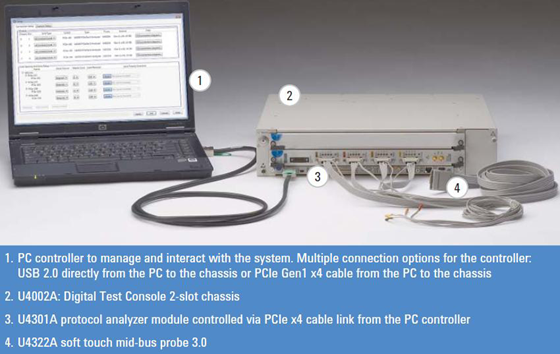

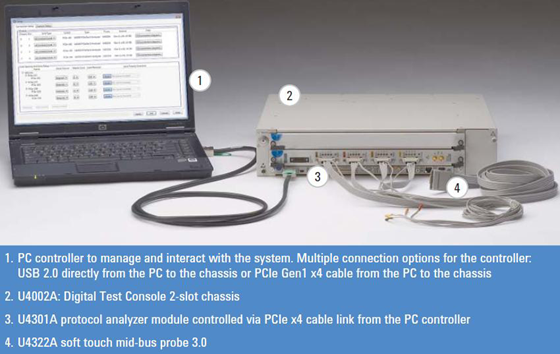

下圖是PCI-e 3.0協(xié)議分析儀U4301A,它是一塊采用了Agilent AXIe架構(gòu)的插卡���,可以插在AXIe的機箱里���,通過探頭來捕獲高速的PCI-e 3.0信號,并通過外部PC控制顯示協(xié)議分析的結(jié)果�。

AXIe是Agilent最新推出的高速模塊化儀器的架構(gòu),除了能給高性能的模塊提供穩(wěn)定可靠的機箱環(huán)境以外�����,還提供了背板的高速數(shù)據(jù)交換能力�,主要用于需要大量數(shù)據(jù)處理的高性能板卡。除了PCI-e 3.0的協(xié)議分析儀以外�����,Agilent在這個平臺上還推出了業(yè)內(nèi)最高性能的U4154A高速邏輯分析儀模塊(可以用于DDR3的協(xié)議測試,支持高達4Gb/s的數(shù)據(jù)速率)���、U4998A高速HDMI協(xié)議分析儀(支持HDMI1.4的測試)���、M8190A高性能任意波發(fā)生器(12G/s采樣率@12位分辨率或8G/s采樣率@14位分辨率)等,因此用戶在這個統(tǒng)一的平臺上可以完成未來的很多高速總線的測試任務����。1塊U4301A插卡可以支持到X8雙向的PCI-e 3.0/PCI-e2.0/PCI-e1.0的協(xié)議測試�����,2塊卡可以支持X16的測試并提供搞到8GB的存儲深度��。為了支持復雜問題的分析和定位����,U4301A還支持多達4級的觸發(fā)序列并預先定了多種錯誤觸發(fā)條件,可以幫助用戶快速發(fā)現(xiàn)總線上的錯誤����。

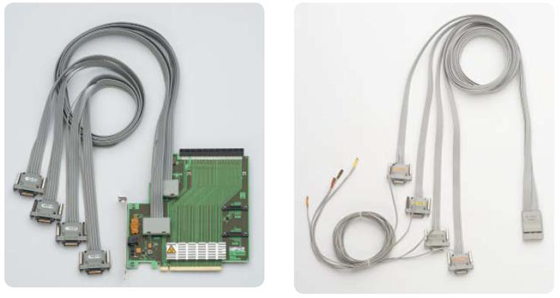

要針對高速的PCI-e 3.0信號做正確的協(xié)議分析,可靠的探頭連接必不可少���。由于PCI-e 3.0的信號經(jīng)過PCB傳輸后信號質(zhì)量惡化很大��,因此PCI-e 3.0的接收芯片內(nèi)部有均衡電路來保證信號的可靠接收����。而對于協(xié)議分析儀的探頭來說也存在同樣的問題,即如果不做均衡可能就無法可靠捕獲總線上的信號�。因此針對PCI-e 3.0的協(xié)議測試,Agilent還提供了帶均衡功能的探頭�����,以下分別是針對計算機應用和嵌入式應用提供的2種探頭����。

很多時候僅僅被動地做總線上的協(xié)議捕獲和分析并不能全面驗證系統(tǒng)在各種未知條件下可能出現(xiàn)的問題,因為實際的測試環(huán)境能夠模擬出來的條件都是有限的���。為了進行更全面的測試���,Agilent還提供了PCI-e 3.0的協(xié)議訓練器U4305A。所謂訓練器���,就是可以人為設(shè)定要發(fā)送的PCI-e數(shù)據(jù)包的內(nèi)容來主動和被測件進行協(xié)議交互以更全面驗證系統(tǒng)功能的儀器��。U4305A設(shè)計成一個PCI-e 3.0的插卡類型�,通過USB接口用外部PC進行控制,可以直接插在主板的PCI-e插槽上進行主板測試��,也可以通過測試背板進行PCI-e插卡的測試���。U4305A還集成了LTSSM的自動測試功能�����,可以快速發(fā)現(xiàn)系統(tǒng)在鏈路協(xié)商中的問題�����。下圖是U4305A及做LTSSM測試的界面。

4. 總結(jié)

綜上所述��,PCI-e 3.0是新一代的高速總線�,采用了很多和前一代完全不一樣的技術(shù)來克服高速數(shù)據(jù)傳輸?shù)男盘栙|(zhì)量問題,也帶來很多全新的測試挑戰(zhàn)�����。Agilent作為PCI-SIG的董事會成員之一��,一直積極參與到PCI-e 3.0的規(guī)范制定和測試方法的實施中,并提供了覆蓋發(fā)送信號質(zhì)量測試�����、接收容限測試�、協(xié)議分析、訓練器等全套的測試方案�����。